# Toward Biorealistic Silicon Neural Circuits on Reconfigurable Platforms

Swagat Bhattacharyya, Pranav O. Mathews, Praveen Raj Ayyappan, and Jennifer O. Hasler

School of Electrical and Computer Engineering

Georgia Institute of Technology

Atlanta, GA 30332

{sbhattac8,pmathews30,payyappan3}@gatech.edu and jennifer.hasler@ece.gatech.edu

Abstract—Reconfigurable analog hardware presents an ideal platform for the realization and analysis of biorealistic neural systems. This work explains the use of subthreshold MOSFETs to model biological channels and proposes energy-efficient, bioinspired neuron and synapse circuits for reconfigurable analog hardware. The proposed circuits are experimentally evaluated in the context of a two-neuron oscillator on an in-house SoC field-programmable analog array in a 350 nm CMOS process.

### I. NEED FOR BIOREALISM AND RECONFIGURABILITY

Biological neurons perform efficient computation with complex nonlinear dynamics, enabling networks of neurons to form synfire chains and winner-take-all circuits, solving problems including path planning and coincidence detection. Neuron models need to be biorealistic to harness dynamical complexities; however, many computing applications are energy-constrained, which poses a challenge while scaling biorealistic neurons to large problems.

Analog implementations are advantageous due to their significantly lower power consumption as compared to their digital counterparts. Hardware-based networks of neurons can facilitate low-level exploration of neural mechanisms [1, 2] and bridge the gap between damaged biological neurons and functional networks [3]. We propose a pathway to improve the emulation of networks of neurons in reconfigurable hardware by modelling biological elements with analog circuits. Our approach capitalizes on the physics of subthreshold MOSFETs to efficiently and accurately implement neural circuits within a low-power, continuous-time CMOS framework [1].

For experimental measurement, we utilize our in-house SoC field-programmable analog array (FPAA), which is a highly versatile general-purpose analog computation platform in a 350 nm process [4] that uses software tools openly available at https://hasler.ece.gatech.edu/FPAAtool/. The FPAA enables flexible network design and 13-bit precision in weights and biases [5]. We also exploit our routing fabric for synaptic computation. While our prior work established a biorealistic Hodgkin-Huxley neuron circuit [6] and a triangle generator circuit [7] to potentially produce excitatory post-synaptic potentials (EPSPs) [8] on our SoC FPAA, networks of neurons have not yet been demonstrated due to inadequate neuron dynamics and triangle generator output waveform scaling in

This material is based on work partially supported by the National Science Foundation Graduate Research Fellowship under Grant No. DGE-2039655.

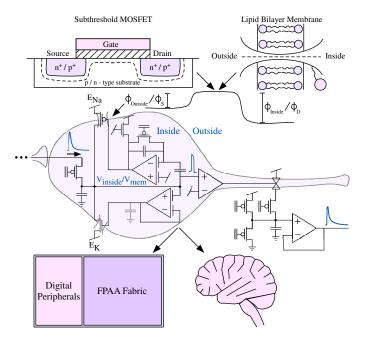

Fig. 1. There are striking similarities between the physics of subthreshold MOS transistors and biological channels, which both modulate channel current between two regions via a gating function that controls the surface potential. This enables one to efficiently model biological neurons in standard CMOS and construct large networks of neurons on reconfigurable analog platforms.

previous attempts. This work addresses and overcomes these issues to experimentally demonstrate a functional network.

To this end, this paper introduces modifications to a previously proposed neuron circuit [6] to enhance dynamics and proposes a new triangle generator circuit with appropriate output scaling for accurate EPSP production. Circuits are constructed and experimentally characterized individually and then together (in the context of a two-neuron oscillator). The rest of this work is structured as follows. Section II relates biological and transistor channels, Section IV explains EPSP generation, Section V shows the dynamics of a two-neuron oscillator, and Section VI provides concluding remarks.

# II. PASSIVE CHANNELS

The physical laws governing the behavior of biological and subthreshold MOSFET channels are similar, as shown in Fig. 1, which enables subthreshold MOSFETs to be an energyefficient means to model biological channels. Fundamentally, in all electrochemical systems, currents flow due to differences in quasi-Fermi levels. In electronics, band diagrams represent increasing electron energy, and for ions, band diagrams represent increasing positive charge energy. Subthreshold MOS-FETs and biological channels share equivalent electronic band diagrams [9], where charges at the edge terminals are modulated by the channel potential. The channel potential  $(\Psi)$  is roughly flat for subthreshold MOSFET channels and varies slightly for biological channels. Both channel types have a Boltzmann distribution of charge carrier states, where the probability of a charge carrier energy state is given by  $p(E) \propto \exp(-E/k_BT)$ , where  $k_BT$  is the mean carrier thermal energy.  $\Psi$  is controlled by some gating mechanism, which is effectively intrinsically fixed for a passive channel and modulated by an external potential or chemical concentration for an active channel. Understanding of passive biological channels helps better understanding of active channels.

A MOSFET modulates the channel current between the source  $(V_s)$  and drain  $(V_d)$  terminal using its gate  $(V_g)$ . The EKV model [9] describes the channel currents for a pFET (well at VDD) and an nFET (substrate at 0 V) as follows:

$$I_p(V_s, V_g, V_d, W/L) = I_{0,p} \frac{W}{L} \left[ e^{-\kappa_p V_g} \left( e^{V_s} - e^{V_d} \right) \right]$$

(1)

$$I_n(V_d, V_g, V_s, W/L) = I_{0,n} \frac{\bar{W}}{L} \left[ e^{\kappa_n V_g} \left( e^{-V_s} - e^{-V_d} \right) \right]$$

(2)

where voltages are normalized by thermal voltage  $U_T = k_B T/q = RT/F$ , W/L denotes the FET dimension ratio,  $\kappa$ : denotes the respective gate-channel coupling strength, and:

$$I_{0,p} = I_{TH,p} \exp\left(\kappa_p \left(\text{VDD} - V_{T0,p}\right) - \text{VDD}\right) \tag{3}$$

$$I_{0,n} = I_{TH,n} \exp\left(-\kappa_n V_{T0,n}\right) \tag{4}$$

where  $I_{TH,:}$  denotes the threshold current, and  $V_{T0,:}$  denotes the threshold voltage of the corresponding device.

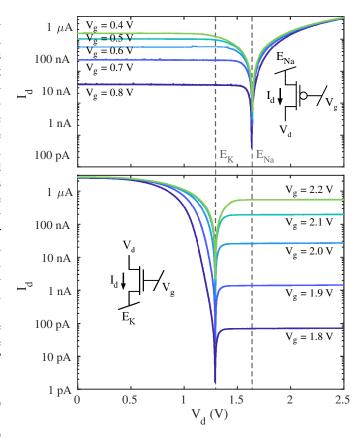

Irrespective of the differing majority carriers of nFETs and pFETs, the underlying principles governing the channel currents are similar; thus, most concepts applicable to pFETs are also applicable to nFETs. Assuming that the pFET source is connected to  $E_{Na}$ , Eq. 1 shows that a pFET transitions smoothly from a conductance to a current source when  $V_d$  continues to drop below  $V_s$ , as expected from biological channels and shown in Fig. 2. At low potential differences between  $V_d$  and  $V_s$  ( $< U_T$ ), the channel acts like a resistor. At higher potentials ( $> 2U_T$ ), the channel potential is only weakly dependent on  $V_d$ ; in such cases, the transistor operates like a current source relative to  $V_d$ , and dependence of the drain current on  $V_d$  can usually be neglected.

# III. NEURON CIRCUIT

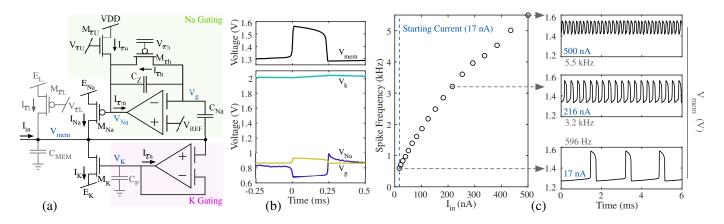

As shown in Fig. 3(a), we use a MOSFET-based neuron with voltage-gated K<sup>+</sup> and Na<sup>+</sup> channels for a biorealistic SoC FPAA implementation [6]. The K<sup>+</sup> channel can only be activated while the Na<sup>+</sup> channel can be both activated and deactivated; thus, the K<sup>+</sup> and Na<sup>+</sup> channel gating behaviors can

Fig. 2. Experimentally measured drain sweeps for a passive (a) pFET channel with  $E_{Na}=1.6\,\mathrm{V}$  and (b) nFET channel with  $E_{K}=1.3\,\mathrm{V}$ . The pFET and nFET correspond to  $M_{Na}$ , and  $M_{K}$ , respectively, which are ion channels present in the neuron circuit model. As explained in Fig. 1, the I-V curves of biological ion channels are similar in shape to these transistor measurements, with the minimum current occurring at the reversal/resting potential.

be represented by a lowpass filter (LPF) and bandpass filter (BPF) response (respectively) and implemented with filters that respond to changes in  $V_{mem}$ .

Tunable elements are necessary to combat mismatch, induce different synaptic weights, and make inter-neuron connections. The reconfigurable SoC FPAA, which utilizes programmable floating-gate (FG) transistors [4], uses FG pFETs as flexible synaptic inputs and precise biases in the channel gating circuits as in [7]. The following subsections discuss how FG-based circuits are leveraged for biorealistic channel gating.

# A. K+ Channel

The nFET-based K<sup>+</sup> channel is gated by a voltage  $V_K$ , which is generated by a nonlinear LPF with a pseudo-first-order response. This LPF is built using an FG operational transconductance amplifier (FGOTA) in a negative feedback configuration and parasitic capacitances on the FGOTA output node. The time constant of the LPF, which is analogous to  $\tau_n$  in the original model of Hodgkin and Huxley [10], can be adjusted via the programmable FGOTA bias current.

$\tau_n$  must be on the timescale of a spike width for biorealism, as shown in Fig. 3(b). The  $\tau_n$  for the neuron tuning in Fig. 3(b) is achieved with an FGOTA bias of only 2 nA; hence, K<sup>+</sup>

Fig. 3. Neuron (a) schematic, (b) experimentally measured nodal voltages during a spike, and (c) experimentally measured IF curve with exemplary  $V_{mem}$ . For the demonstrated tuning, 17 nA initiates continuous firing, which starts at 596 Hz and can be modulated by an order of magnitude. Notice that the spike shape and minimum level changes with the firing rate. Also note that in (a), grayed components are induced through parasitics.

gating draws little power. The DC level of  $V_K$ , which can be adjusted by programming a gate charge discrepancy between the input FG differential pair transistors of the FGOTA, must be large enough to pull down  $V_{mem}$  during repolarization but low enough to allow the Na<sup>+</sup> channel to initiate depolarization.

### B. Na<sup>+</sup> Channel

The pFET-based Na<sup>+</sup> channel is gated by a voltage  $V_{Na}$ , which is generated by a nonlinear BPF with a pseudo-second-order response. The BPF has a smaller time constant  $\tau_m$ , which is adjusted via the FGOTA bias current, and a larger time constant  $\tau_h$ , which is adjusted via  $V_{\tau h}$  (the programmed gate voltage on the feedback FG pFET  $M_{\tau h}$ ).  $\tau_h$  must not be excessively large, as this prevents neuron repolarization.  $V_{REF}$ , which sets the DC level of  $V_{Na}$ , should be chosen such that  $M_{\tau h}$  will have sufficient strength to pull current from the output node, changing  $V_{Na}$ . We have also added  $M_{\tau U}$ , an nFET "constant-current source," to the original circuit in [6] to restrict the lower amplitude level of  $V_{Na}$ , ensuring consistent spiking while preserving biological dynamics.

Neuron behavior can be elucidated by studying the waveforms in Fig. 3(b). When a fast-rising voltage is sensed at  $V_{mem}$  above the high-frequency corner set by  $\tau_m$  (e.g., due to a sufficiently large input current  $I_{in}$ ),  $V_{Na}$  drops, sourcing current into  $V_{mem}$  and causing a depolarization.  $V_{Na}$  rises back after some time, deactivating the Na<sup>+</sup> channel. The K<sup>+</sup> channel, which slowly activates in response to the depolarization, cooperates with the Na<sup>+</sup> deactivation to repolarize  $V_{mem}$ . Note that  $V_{Na}$  overshoots on its way back up, which leads to a biorealistic hyperpolarization.

# C. Neuron Characterization

The neuron IF curve shape governs network dynamical behavior. Fig. 3(c) displays the IF curve of the tuned neurons used in this work. The onset of periodic spiking occurs above a threshold of  $17 \,\mathrm{nA}$ , and spiking frequency initially increases linearly with input current ( $I_{in}$ ) before tapering. Intermittent spiking can be induced by noise even when  $I_{in}$  is below the periodic spiking threshold. The shape of action potentials varies

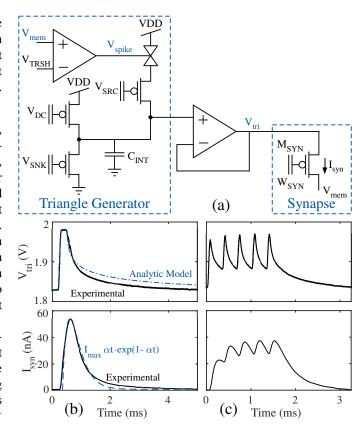

Fig. 4. (a) Triangle generator and source-coupled synapse schematics. (b)  $V_{tri}$  and EPSP  $(I_{syn})$  after a spike. Measurements of  $V_{tri}$  match well with Eq. 6, and measured EPSPs closely model the Rall Alpha function. (c)  $V_{tri}$  and  $I_{syn}$  measurements during a spike burst demonstrating EPSP stacking.

with the  $I_{in}$ , with lower  $I_{in}$  having larger inter-spike intervals and reaching lower potentials during hyperpolarization.

# IV. GENERATION OF POSTSYNAPTIC POTENTIALS

Neuron depolarizations are detected using a comparator with a threshold  $V_{TRSH}$ . To ensure the comparator output  $(V_{spike})$  can reliably feed the corresponding triangle gener-

ator circuit across all spiking frequencies, action potentials should be thresholded near the "kink" caused by Na+ channel deactivation during repolarization. The triangle generator and synapse [Fig. 4(a)] then cooperatively generate an EPSP from  $V_{spike}$ . This work uses source-coupled FG pFET synapses, where the synapse strength can be adjusted by programming the FG using hot electron injection. We operate synapses in subthreshold saturation, where the drain current varies exponentially with the source voltage. Since an EPSP resembles a smoothed piecewise combination of a fast-growing and a slow-decaying exponential, an EPSP can be generated by modulating the source voltage of a synapse using an asymmetric triangular waveform. We generate this triangular waveform by asymmetrically integrating  $V_{spike}$  using the circuit in Fig. 4(a). The output of this circuit rises rapidly to a high level when  $V_{spike}$  is high and falls slowly to a resting DC level when  $V_{spike}$  is low. The T-gate responsible for switching the attack current is placed above  $M_{SRC}$  to mitigate charge injection into the integration node.

Triangle generator behavior can be better understood by writing a compact ODE for the integration node using KCL and Eq. 1 for channel currents, assuming matched dimensions and threshold voltages for  $M_{DC}$ ,  $M_{SRC}$ , and  $M_{SNK}$ :

$$\frac{\partial V_{tri}}{\partial t} = \frac{M_{DC}I_{0,p}}{C_{INT}U_{T}} \left[ \epsilon e^{-k_{p}V_{SRC}} \left( e^{\text{VDD}} - e^{V_{tri}} \right) + e^{-k_{p}V_{DC}} \left( e^{\text{VDD}} - e^{V_{tri}} \right) - e^{-k_{p}V_{SNK}} \left( e^{V_{tri}} - 1 \right) \right]$$

(5)

where voltages are normalized by  $U_T$ , and  $\epsilon=1$  if  $V_{spike}$  is high, and  $\epsilon=0$  otherwise. As VDD  $\gg V_{tri}\gg 0$ ,  $\partial V_{tri}/\partial t\approx$

$$\frac{M_{DC}I_{0,p}}{C_{INT}U_{T}}\left[e^{\text{VDD}}\left(\epsilon e^{-k_{p}V_{SRC}}+e^{-k_{p}V_{DC}}\right)-e^{V_{tri}-k_{p}V_{SNK}}\right] \tag{6}$$

Typically, the triangle generator is biased with  $V_{SRC} \ll V_{SNK} \ll V_{DC}$ . We can consequently find that the resting DC level  $(V_{tri,min})$ , swing range  $(\Delta V_{tri})$ , and initial decay rate of  $V_{tri}$   $(S_{dec})$  depend on the programmed FG voltages:

$$V_{tri,min} \approx \text{VDD} + k_p \left( V_{SNK} - V_{DC} \right)$$

(7)

$$\Delta V_{tri} \approx k_p \left( V_{DC} - V_{SC} \right) \tag{8}$$

$$S_{dec} = -M_{DC}I_{0,p} \exp\left(V_{tri} - k_p V_{SNK}\right) / U_T C_{INT}$$

(9)

The initial slew rate of  $V_{tri}$  is only a weakly nonlinear function of  $V_{tri}$ , and although the asymptotic slew rate magnitude is lower than what is predicted from Eq. 9, this nonideality has a minimal effect on the EPSP shape since the correponding current magnitudes are small. For a "fast" attack bias, such as in the tuning in Fig. 3(b), parasitic capacitances on the FPAA are usually the most significant contributors to the duration of the rising portion of the EPSP, not  $V_{SRC}$ .

Triangle generator tuning depends on the neuron IF curve; a convenient protocol for tuning the triangle generator is to: (1) adjust  $V_{SNK}$  so the decay rate is 4-5 times lower than the attack rate but does not induce EPSP stacking at the lower end of the neuron IF curve, (2) adjust  $V_{DC}$  so the desired resting DC level lies between 1.8 V and 2.0 V, and (3) adjust  $V_{SC}$  so

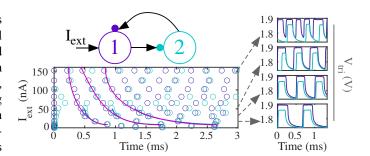

Fig. 5. Experimentally measured spike times from a two-neuron oscillator for different  $I_{ext}$  along with exemplary triangle generator outputs. Neuron 1 spikes regularly above some threshold current. For low  $I_{ext}$ , neuron 2 is synchronized with neuron 1. Beyond a certain  $I_{ext}$ , neuron 2 becomes asynchronous since bounds on synaptic strength prevent neuron 2 from spiking as fast as neuron 1, even with EPSP stacking.

the swing range lies between  $4U_T$  and  $8U_T$ . Iterating steps 1-3 a few times yields a reasonable tuning. Measurements from a tuned triangle generator and excitatory synapse, as shown in Fig. 4(b), indicate that  $V_{tri}$  closely follows Eq. 6, and the EPSP closely approximates a Rall Alpha function. Additionally, Fig. 4(c) demonstrates EPSP stacking during fast spiking, which is essential for network dynamics and is observed both in biology and our hardware implementation.

# V. Two-Neuron Oscillator

Neuronal oscillators are ubiquitous in motor neuron pathways and can serve as a benchmark for evaluating neuron dynamics. One-dimensional oscillators can be constructed using a feedforward chain of neurons with a recurrent connection feeding the output back into the input. In this work, we construct a two-neuron oscillator, as depicted in Fig. 5, with all synaptic connections of roughly the same strength. We measure spike timestamps for both neurons and observe that the "fronts" corresponding to the spike timing of neuron 1 form regular patterns (represented by fuchsia lines) regulated mainly by the IF curve of neuron 1. Meanwhile, the fronts corresponding to the spike timing of neuron 2 (represented by blue lines) stay synchronous to neuron 1 for low external input currents  $(I_{ext})$  but become asynchronous for high  $I_{ext}$ despite considerable EPSP stacking. This phenomenon occurs due to limitations imposed by synapse strength, which become unable to match  $I_{ext}$  beyond some limit. While these results demonstrate the effectiveness of our current approaches, additional work is necessary to ensure consistent tuning across all neurons and synapses to guarantee accurate large-scale dynamical behavior in the presence of mismatch.

# VI. CONCLUSION

This work has explored the use of subthreshold MOSFETs to simulate biological channels and has shown neuron and synapse circuits with biophysically-accurate dynamics on an in-house SoC FPAA. Synaptic circuit transients are found to follow analytical models, and circuits are demonstrated in a two-neuron oscillator. In all, this work is a step toward a complete ecosystem for studying biorealistic neural systems.

### REFERENCES

- [1] S. Furber, "Large-scale neuromorphic computing systems," *Journal of Neural Engineering*, vol. 13, no. 5, p. 051001, Aug. 2016. [Online]. Available: https://doi.org/10.1088/1741-2560/13/5/051001

- [2] S. Koziol, P. Hasler, and M. Stilman, "Robot path planning using field programmable analog arrays," in 2012 IEEE International Conference on Robotics and Automation, 2012, pp. 1747–1752.

- [3] F. Khoyratee, F. Grassia, S. Saïghi, and T. Levi, "Optimized real-time biomimetic neural network on FPGA for bio-hybridization," Frontiers in Neuroscience, vol. 13, Apr. 2019. [Online]. Available: https://doi.org/10.3389/fnins.2019.00377

- [4] S. George, S. Kim, S. Shah, J. Hasler, M. Collins, F. Adil, R. Wunderlich, S. Nease, and S. Ramakrishnan, "A programmable and configurable mixed-mode FPAA SoC," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 6, pp. 2253–2261, 2016.

- [5] S. Kim, J. Hasler, and S. George, "Integrated floating-gate programming environment for system-level ICs," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 6, pp. 2244–2252, 2016.

- [6] A. Natarajan and J. Hasler, "Hodgkin–Huxley neuron and FPAA dynamics," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 12, no. 4, pp. 918–926, 2018.

- [7] A. Natarajan and J. Hasler, "Implementation of synapses with Hodgkin Huxley neurons on the FPAA," in 2019 IEEE International Symposium on Circuits and Systems (ISCAS), 2019, pp. 1–5.

- [8] C. Gordon, E. Farquhar, and P. Hasler, "A family of floating-gate adapting synapses based upon transistor channel models," in 2004 IEEE International Symposium on Circuits and Systems (ISCAS), vol. 1, 2004, pp. I–317.

- [9] C. Mead, Analog VLSI and Neural Systems, ser. Addison-Wesley VLSI systems series. Reading, Mass: Addison-Wesley, 1989.

- [10] A. L. Hodkin and A. F. Huxley, "A quantitative description of membrane current and its application to conduction and excitation in nerve," *Bulletin of mathematical biology*, vol. 52, no. 1, pp. 25–71, 1990.